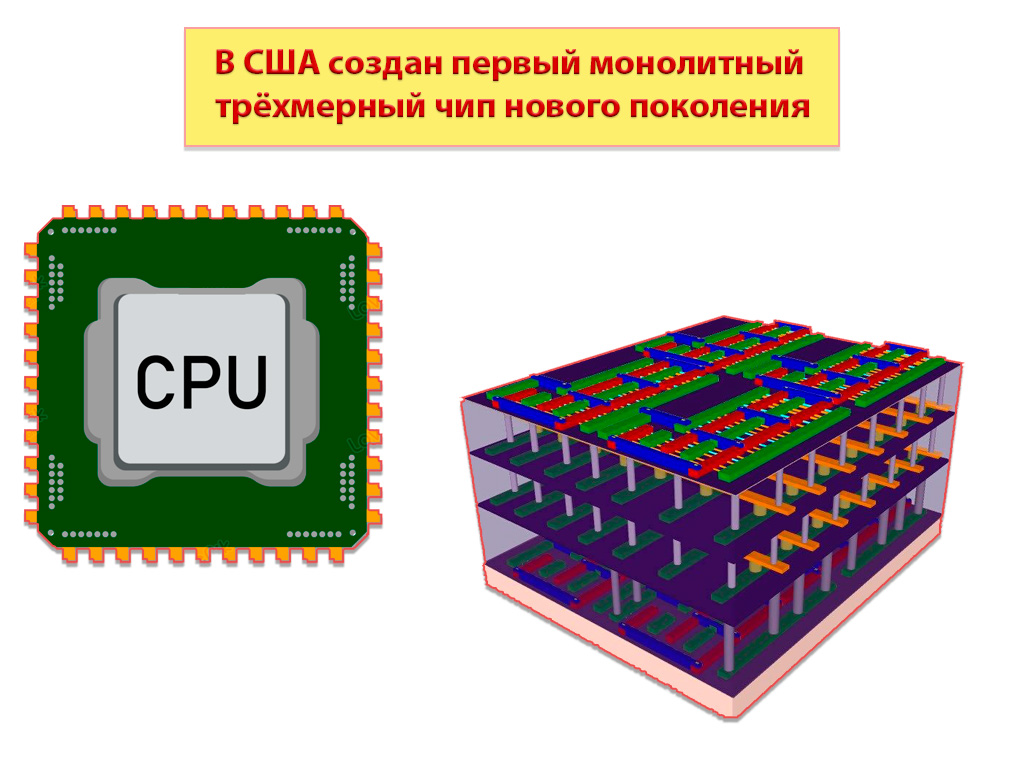

Развитие микроэлектроники всё чаще сталкивается с физическими ограничениями традиционных плоских кристаллов. По мере замедления масштабирования транзисторов инженеры ищут альтернативные подходы к повышению производительности и энергоэффективности. Одним из таких направлений считается трёхмерная интеграция. Недавно группа американских исследователей сообщила о создании первого в мире по-настоящему монолитного 3D-чипа, который объединяет кремниевую логику, резистивную память и транзисторы на основе углеродных нанотрубок.

Над проектом работала совместная команда специалистов из Стэнфордского университета, Университета Карнеги–Меллона, Пенсильванского университета и Массачусетского технологического института. Производство опытного образца было организовано в партнёрстве с компанией SkyWater Technology, что принципиально отличает эту разработку от большинства лабораторных экспериментов.

Ключевая особенность нового чипа заключается в его архитектуре. В отличие от традиционных двухмерных микросхем, где логика и память располагаются в одной плоскости, в данном случае вычислительные и запоминающие элементы размещены вертикально, один над другим, внутри единого кристалла. При этом разработчики не собирали чип из отдельных слоёв, а формировали каждый уровень последовательно на одной кремниевой пластине.

Для этого был использован специальный низкотемпературный технологический процесс, позволяющий добавлять новые слои без повреждения уже сформированных структур. Такой подход дал возможность создать плотную систему вертикальных соединений, значительно сократив расстояние между логикой и памятью и, как следствие, снизив задержки передачи данных.

Прототип был изготовлен на производственных мощностях SkyWater с использованием 200-миллиметровых кремниевых пластин и проверенных техпроцессов уровня 90-130 нм. Несмотря на относительно крупные нормы, чип объединяет несколько типов технологий: классическую CMOS-логику, резистивную оперативную память и полевые транзисторы на базе углеродных нанотрубок. Все этапы производства выполнялись при температуре около 415 °C, что является важным условием для многослойной интеграции.

По результатам аппаратных испытаний исследователи зафиксировали примерно четырёхкратный рост пропускной способности по сравнению с эквивалентной двухмерной реализацией при сопоставимых задержках и габаритах. Дополнительно были проведены расчёты и моделирование более сложных конфигураций с увеличенным числом уровней памяти и вычислительных блоков. В таких сценариях производительность в задачах искусственного интеллекта, включая модели семейства LLaMA, возрастала до 12 раз.

В долгосрочной перспективе авторы проекта считают, что дальнейшее развитие вертикальной интеграции способно обеспечить 100-1000-кратное повышение энергоэффективности, причём без необходимости уменьшения размеров транзисторов. Это делает подход особенно привлекательным на фоне замедления классического масштабирования.

Важно отметить, что ранее экспериментальные 3D-чипы уже демонстрировались в научных лабораториях. Однако данная работа выделяется тем, что была реализована в условиях коммерческого производства, а не на специализированной исследовательской линии. Представители SkyWater подчеркнули, что проект доказывает реальную применимость монолитных 3D-архитектур в промышленности.

Создание монолитного трёхмерного чипа с вертикальной интеграцией логики и памяти можно считать значимым шагом в развитии полупроводниковых технологий. Работа американских исследователей показывает, что 3D-архитектуры способны выйти за пределы академических экспериментов и стать частью реальных производственных процессов. В условиях растущих требований к производительности и энергоэффективности именно такие подходы могут определить направление развития микроэлектроники в ближайшие годы.

Источник:

www.tomshardware.com

0 Комментарий(я)

Зарегистрируйтесь чтобы оставить комментарий